# An FVF-Based Gm-Enhanced fully balanced Preamplifier

Hassan Faraji Baghtash<sup>1\*</sup>, Mona Kargar<sup>2</sup>

<sup>1</sup>Faculty of Electrical Engineering, Sahand University of Technology, Sahand New Town, Tabriz 5331817634, Iran

<sup>1</sup>Email: hfaraji@sut.ac.ir, <sup>2</sup>Email: Mona.kargar@gmail.com

Received: 12/03/2023, Revised: 15/05/2023, Accepted: 14/10/2023.

#### **Abstract**

A High-gain, fully balanced preamplifier is presented. The proposed structure advantages flipped voltage follower scheme to achieve a compact current conveyor with very low input impedance. The presented current conveyor then is used as a core element to realize a high-gain, gm-enhanced trans-conductance amplifier. The presented amplifier is suitable for application as a preamplifier. The high gain of amplifier makes it very suitable to be configured in a feedback form to deliver a high-precision predefined or programmable amplification gain. The proposed structure draws a very low power of 150nW from a 0.6V supply voltage.

The Spectre Post-layout simulations with TSMC 180nm CMOS technology have been performed. The proposed amplifier exhibits an open-loop DC gain of 141.5dB and 3-dB frequency bandwidth of 2.4kHz at 60dB closed-loop configuration. The load capacitance is set to be 5pF. The proposed structure also delivers high CMRR and PSRR values of 148.3dB and 153.7dB, respectively.

## Keywords

FVF, OTA, Low power, Low voltage, CCII, Preamplifier.

### 1. Introduction

Nowadays, technology downscaling, which is driven by digital CMOS technology and accompanied by increasing demand for emerging low-power (LP), low-voltage (LV), and battery-operated devices has enforced the analog designs with some serious challenges [1, 2]. Neighboring with digital systems, the analog circuits must be capable of operating in very reduced supply voltages, the condition which normally is the worst for the performance of analog blocks.

A serious problem faced by analog designers is that as the technology and accordingly the supply voltage is scaled down, the transistor threshold  $(V_{th})$  and saturation (V<sub>ds,sat</sub>) voltages are not scaled down in the same percentage, which causes degradation of transistor parameters [3]. Some of the parameters that majorly affected are voltage dynamic range (DR), intrinsic voltage gain (VG), trans-conductance (Gm), frequency bandwidth (BW), and noise performance (NP). The direct result of degradation of transistor parameters is performance and design validity reduction of circuits. Unfortunately, most of the conventional designs and circuit structures fail to operate appropriately in these stringent conditions. This necessitates revising the old structures and performing some modifications with the intention of making them suitable to operate in a lowvoltage regime. Novel structures are also very welcome. Some efforts in this regard can be found in [4-9].

Operational trans-conductance amplifier (OTA) is one of the most important analog blocks that has a vast application in LP and LV designs. Though, numerous OTA structures have been introduced by the design community to address the needs of low-voltage design areas. Nevertheless, the design of OTA in LV regime is rather challenging. Routinely cascode structure should be avoided as much as possible. Meaning some wellaccepted structure such as folded cascode (FC) OTAs which has shown proven performance (especially in communication circuits) should be discarded or at least majorly revised in design. One general solution may be revising the designs to operate in subthreshold regime. This relaxes most of the problems associated with LV design, yet bring some limits foreground, such as limited speed performance. Among other well-stablished low voltage design techniques are using floating gate [10, 11] and bulk-driven [6, 12, 13] transistors in circuit design. These methods are very effective in reducing the required supply voltage. However, the reduce effective transconductance is the major drawback of these techniques. Though, one of the main problems that must be addressed in the LV OTA designs is to provide sufficiently large Gm. In fact, the application of LV design techniques commonly decreases the effective Gm of structure. Unfortunately, this degrades most of the desired parameters of OTA, such as speed, power, and voltage gain. Some efforts have been made to address this short come [14-20]. For instance, a positive feedback scheme is used in [14] to boost Gm, or current recycling method is utilized by [17, 19, 20] for trans-conductance and slew rate enhancement of folded cascode structures. Yet, each has its own disadvantage. For instance, structures presented in [17, 19, 20] all suffer from reduced output swing range due to the use of cascoding structures. One accepted routine to realize dependable

<sup>&</sup>lt;sup>2</sup>Iranian Space Research Center (ISRC), Tehran, Iran

<sup>\*</sup>Corresponding author

low voltage circuit, is to combine some low voltage techniques in an innovative manner with well-known structure. For example, using body driven transistors in well-known folded cascode structure can effectively extend common mode input range of structure. The reduce gm now can be compensated with current recycling technique which can easily integrated to the structure. Even though this adds some extra power consumption, yet it rather solves most of the problems with low voltage regime design. The only problem remains is its reduced output swing range due to the cascode output stage. This can be tolerated in supply voltages down to 1V. Nevertheless, the structure fails to operate under supply voltages less than 0.5V.

Another important parameter that degrades in LV designs is voltage gain. Beside the straight effect of reduced Gm in structure's voltage gain, this parameter is affected by other consequences, as well. Due to the reduced supply voltage, increasing the gain by cascoding is not applicable in most cases. Though, the only option remains is to use cascading [21, 22]. However, cascading increases the power consumption and design complexity. More importantly, the cascaded structures always require complex compensation networks because of the increase in the number of amplification stages and consequently high-impedance nodes [23].

A new amplifier design concept based on the second generation of current conveyor (CCII) is presented in this work. The proposed structure employs a very compact CCII structure which is especially designed to serve the proposed idea. The proposed CCII utilizes the flipped voltage follower structure to deliver some everinteresting parameters such as low input impedance and high output impedance under very reduced power consumption. Thanks to the novel structure and compact circuit realization, the proposed structure succeeds in delivering some improved specifications. Indeed, the structure employs both cascoding and cascading to achieve very high gain values. It uses three cascading stages to boost the gain. Nevertheless, one stage of this cascading is imbedded in to the flipped voltage follower (FVF) structure that ease the compensation effort considerably. The proposed structure avoids the cascode branch in output stage to maximize the output swing range. However, the input common mode range is limited due to the use of no especial low voltage technique. Fortunately, this is not a serious challenge as it can be solved, if required, by applying some known techniques such as using bulk driven transistors.

The paper is organized into four sections. After introduction in section 1, section 2 describes the circuit realization and its performance. In section 3 the simulation results are presented. Finally, section 4 concludes the paper.

# 2. The proposed amplifier

# 2.1. FVF-based differential input stage

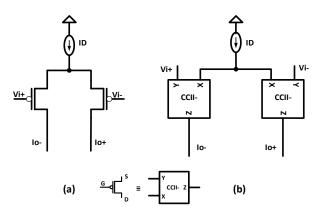

The differential input stage is an essential building block in any amplifier structure. This stage, conventionally, is realized by two input-transistors and a tail current (Fig. 1a). This block converts differential and even singleended voltage signals to differential current signals, effectively. Despite some limitations such as restricted slew rate and reduced voltage headroom due to the  $V_{\rm ds}$  requirement by the tail current, this structure, still, is very promising in amplifier structures. Here, we will look from another perspective at this block and will try to redesign it for better functionality.

Fig.1. (a) The conventional differential input stage, (b) The current conveyor-based realization of (a)

Each transistor in Fig. 1a can be regarded as a second-generation current conveyor (CCII), where in, the terminals of gate, source, and drain correspond to Y, X, and Z terminals in CCII. Though, Fig. 1a can be redrawn as Fig. 1b.

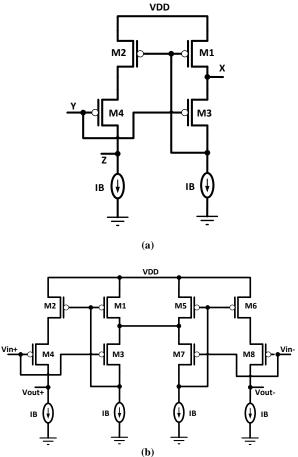

The problem with transistors is that their characteristics are determined by technology parameters, while for the CCII, they can be set by various circuit realizations, providing extra degree of freedom for designer. For example, the trans-conductance and the voltage gain of transistor are intrinsic and given by gm and gmro, respectively, while for CCII, they are given by 1/r<sub>x</sub> and  $R_o/r_x$ ; where  $r_x$  and  $R_o$  are input and output impedance of CCII, respectively. Our goal is to advantage this perspective to configure an input stage with enhance trans-conductance and voltage gain, the degraded parameters in modern technologies. Therefore, if we can manage to have a CCII structure with  $r_x < 1/g_m$  and  $R_o > r_o$ , we can configure an input stage with trans-conductance and voltage gain higher than gm and g<sub>m</sub>r<sub>o</sub>, respectively. Nevertheless, all CCII structures are not suitable for this goal. It must be kept as simple as possible to preserve the simplicity of the traditional differential input stage. More importantly, is its frequency characteristics, which should avoid any low frequency zero and poles. Otherwise, the frequency characteristics of overall amplifier may be degraded drastically. Here we propose a CCII structure which can serve well for the purpose of writing, a flipped voltage follower (FVF) based structure. The FVF-based CCII and the proposed FVF-based differential input stage are shown in parts (a) and (b) of Fig. 2, respectively. Enjoying from FVF structure, the proposed CCII presents a reduced input resistance r<sub>x</sub> of 1/g<sub>m</sub><sup>2</sup>r<sub>o</sub> and increased output resistance and voltage gain of  $g_m r_o^2$  and  $g_m^3 r_o^3$ , respectively. Interestingly, the frequency characteristics of FVF structure is also very promising, where in, the non-dominant poles are located at far beyond unity gain frequency (UGF). Besides, the power consumption is well-kept under control. It is worth noting that, although the power consumption of input stage is almost doubled, however, as this stage consumes

a small fraction of overall amplifiers' power, the power consumption of the whole amplifier does not affect much.

Fig. 2. (a) FVF-based CCII, (b) differential input stage based on FVF-based CCII

To further discuss the performance of FVF-based differential input stage, let us assume that a differential signal is applied to its inputs. This differential signal deviates the structure from balanced condition and causes a current flowing from M1 to M5. This current is mirrored by M2 and M6 correspondingly and delivered to the outputs through M4 and M8. As the X node impedance of FVF structure is very low (1/g<sub>m</sub><sup>2</sup>r<sub>o</sub>), the signal due to the differential input voltage will be considerably high (about g<sub>m</sub><sup>2</sup>r<sub>o</sub>). Now consider we apply a common mode signal to structure's inputs. At this condition, due to the large degeneration output resistors of M1 and M5, the current signal that is generated and then transferred to the structure's outputs will be extremely low (ideally zero). This promises a very high value of CMRR for the proposed FVF-based differential input stage.

The transistor-level realization of the proposed FVF-based gm-enhanced amplifier is presented in the following section.

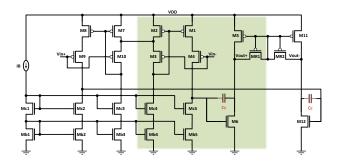

Fig. 3. Transistor level implementation of the proposed amplifier

# 2.2. Proposed FVF-based gm-enhanced amplifier

The transistor-level realization of the proposed FVFbased gm-enhanced amplifier is depicted in Fig. 3. One half-circuit of the overall fully differential structure is shaded in the picture (of Fig. 3), which is composed of compensation capacitor of Cc and transistors M1-M6, Mc4-Mc5, Mb4-Mb5, and MR1. Considering one halfcircuit of the structure (the shaded one), transistors M1-M4 in coordination with biasing transistors of Mc4-Mc5 and Mb4-Mb5 configure the first stage of amplifier. Whereas the transistors M5-M6 configure the second stage. The transistor MR1 with the help of MR2 (its counterpart in other half-circuit) configures local common-mode feedback to separate the common mode signal from differential mode one and also to set the common mode voltage at proper voltage value. The two half-circuits of structure act in a collaborative manner to configure fully differential well-balanced amplifier structure. Performing some calculations, the commonmode and differential-mode voltage gains are given by the following relations for the whole amplifier. By calculating the output voltages for differential mode and common mode voltages from (1) and (2) respectively, we can obtain the differential mode and common mode voltage gains given by (3) and (4), respectively. In fully differential amplifiers, the common mode voltage gain is obtained by calculating the voltage gain for either positive or negative output voltage; here, we used the positive voltage for this sake.

These relations show that the differential mode voltage gain is given by  $(g_m r_o)^4$ , approximately; while the common mode gain can be reached to zero, providing that a perfect matching between M1 and M2 can be made. Even if we consider a 10% mismatch between these two transistors, the common mode voltage gain is given by  $(g_m r_o)/10$ , approximately. This is at least 4 orders of magnitude less than differential mode voltage gain, approximately. These calculations promise very high attainable CMRR values.

$$\frac{V_{out+}}{V_{id}} \Box \frac{1}{2} g_{m1} g_{m3} g_{m6} r_{o3} \left( g_{m4} r_{o1} r_{o4} \parallel g_{mc5} r_{ob5} r_{oc5} \right) \left( r_{o5} \parallel r_{o6} \right) \\

\frac{V_{out-}}{V_{out-}} \Box -\frac{1}{2} g_{m8} g_{m10} g_{m12} r_{o10} \left( g_{m9} r_{o8} r_{o9} \parallel g_{mc2} r_{ob2} r_{oc2} \right) \left( r_{o12} \parallel r_{o11} \right)$$

(1)

$$\frac{V_{out+}}{V_{ic}} \Box \frac{g_{m6}}{g_{m5}} \left( \frac{1}{r_{o1}} - \frac{g_{m1}}{g_{m2}r_{o2}} \right) \left( g_{m4}r_{o1}r_{o4} \parallel g_{mc5}r_{ob5}r_{oc5} \right) \\

\frac{V_{out-}}{V_{ic}} \Box \frac{g_{m12}}{g_{m11}} \left( \frac{1}{r_{o8}} - \frac{g_{m8}}{g_{m7}r_{o7}} \right) \left( g_{m9}r_{o8}r_{o9} \parallel g_{mc2}r_{ob2}r_{oc2} \right)$$

(2)

$$A_{vd} = \frac{V_{out+} - V_{out-}}{V_{id}} \square \frac{1}{2} g_{m1} g_{m3} g_{m6} r_{o3} (g_{m4} r_{o1} r_{o4} \parallel g_{mc5} r_{ob5} r_{oc5}) (r_{o5} \parallel r_{o6}) + \frac{1}{2} g_{m8} g_{m10} g_{m12} r_{o10} (g_{m9} r_{o8} r_{o9} \parallel g_{mc2} r_{ob2} r_{oc2}) (r_{o12} \parallel r_{o11})$$

$$(3)$$

$$A_{vc} = \frac{V_{out-}}{V_{ic}} = \frac{V_{out+}}{V_{ic}} \square \frac{g_{m6}}{g_{m5}} \left( \frac{1}{r_{o1}} - \frac{g_{m1}}{g_{m2}r_{o2}} \right) \left( g_{m4}r_{o1}r_{o4} \parallel g_{mc5}r_{ob5}r_{oc5} \right)$$

$$(4)$$

$$A_{vc} = \frac{V_{out-}}{V_{ic}} = \frac{V_{out+}}{V_{ic}} \left[ \frac{g_{m6}}{g_{m5}} \left( \frac{1}{r_{o1}} - \frac{g_{m1}}{g_{m2}r_{o2}} \right) \left( g_{m4}r_{o1}r_{o4} \parallel g_{mc5}r_{ob5}r_{oc5} \right) \right]$$

$$\overline{V_{n,in}}^{2} \left[ \frac{\overline{I_{1,n}}^{2} + \overline{I_{B4,n}}^{2} + \overline{I_{B5,n}}^{2}}{g_{m1}^{2} g_{m3}^{2} g_{mc4}^{2} r_{dsc4}^{2} r_{dsb4}^{2}} + \frac{\overline{I_{4,n}}^{2}}{g_{m1}^{2} g_{m3}^{2} g_{mc4}^{2} r_{dsc4}^{2} r_{dsc4}^{2} r_{dsc4}^{2}} + \frac{\overline{I_{3,n}}^{2}}{2g_{m3}^{2}} \right]$$

$$(5)$$

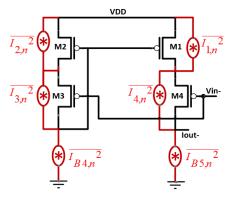

# 2.3. Noise Analysis

It is well-established that the noise performance of the two-stage circuit is dominated by the first stage. To this end, the noise contributors in the half-circuit of the first stage are depicted in Fig. 4. Using the schematic of Fig. 4, the input referred noise voltage is given as (5).

The relation (5) shows that the noise performance of structure is mainly dominated by input-transistor M3 (M10). The noise contribution of transistor M2 (M7) is eliminated from the outputs due to its common mode appearance, thus generates no differential signal in the output.

Fig. 4. The half-circuit noise model for the input stage of proposed structure

# 2.4. The common-mode feedback, compensation

In general, any fully differential structure needs a common-mode feedback circuit to stabilize the output common mode voltage of the overall structure. The reason behind is that unlike for the single-ended amplifiers, for differential output amplifiers the general feedback fails to stabilize the output common-mode voltages. In the proposed structure, the CMFB circuit is accomplished by the MR1 and MR2 which act as large resistors and average and feed the common-mode signal back to the circuit. The CMFB circuit employed in the proposed structure is absolutely power and area efficient. It introduces no extra power to the circuit. Besides, the large resistors are implemented with two small transistors that occupy negligible area. In addition to CMFB in the output stage, the circuit effectively suppresses the common mode input signals, as well. As is discussed in previous section, the common mode signals experience very low amplification gain compared to the differential mode ones. Referring to the schematic of the proposed circuit in Fig. 3, the dominant poles of amplifier can be estimated intuitively. In brief, the two most dominant poles of the structure are estimated to be located at gate and drain of M6 (M12). The first pole which is located at the gate of M6 (M12), is mainly due to the very large output impedance seen from this node and relatively large capacitance of M6 (M12). This pole value is about  $P_1$ =- $1/(r_{o1}r_{o4}g_{m4}|/r_{ob5}r_{oc5}g_{mc5})(C_{gs6}+C_{gd6}(1+g_{m6}(r_{o6}|/r_{o5})))$ . The second pole is mainly due to the large load capacitance and relatively large output impedance. This pole value is about  $P_2=-1/(r_{o6}/|r_{o5})C_L$ . The proposed circuit simply adopts the miller compensation network to compensate the circuit for desired phase margin at required amplification gain  $(C_C=1pF)$ . Applying compensation relocates the poles  $P_1$ '=- $1/(r_{o1}r_{o4}g_{m4}/|r_{ob5}r_{oc5}g_{mc5})(C_{gs6}+(Cc+C_{gd6})(1+g_{m6}(r_{o6}/|r_{o5})))$ and  $P_2'=-g_{m6}/C_L$ , respectively. It is worth noting that as the proposed circuit is devoted for application as preamplifier stage in signal acquisition systems, it will not be compensated for unity-gain feedback condition. This enables the structure to achieve very high operating bandwidth under reduced power consumption along with precise amplification gain; thanks to its very high open loop gain. Yet, it is worth noting that the compensating for unity-gain feedback condition would require large capacitors in compensation network. Which fortunately is not applicable to the current design due to its target application.

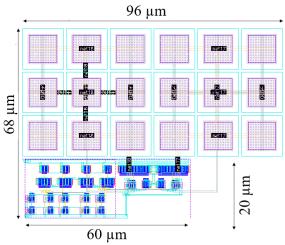

Fig. 5. The layout view of the proposed current push-pull based OTA

# 3. Simulation Results

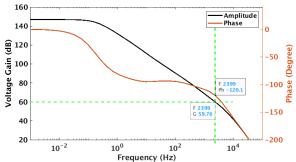

The post-layout simulations are carried out using TSMC 180nm, MS/RF, 1P6M, CMOS technology utilizing 0.6V power supply. The transistor aspect ratios and bias current are provided in Table I. The layout view of the proposed structure is given in Fig. 5. The structure occupies about 0.006 mm<sup>2</sup> with a core area of 0.001 mm<sup>2</sup>. Due to the low supply voltage and very low biasing currents, all transistors are forced to operate in subthreshold region. The frequency performance is plotted in Fig. 6. This figure shows the magnitude and phase of the amplifier over the frequency range. From this figure, the DC gain of the proposed OTA is evaluated to be 141.5dB. As is stated earlier, the circuit is proposed to be used as a preamplifier in applications with high and precise voltage gains. Therefore, the phase margin should be checked for 60 dB which is the gain of feedback loop. Hence, here the amplifier is compensated for 60 dB feedback gain. This prevents bandwidth reduction due to unnecessary compensation for unity gain configuration. The feedback network can simply be realized by capacitors or resistors (here 10 pF and 10 fF capacitors).

Table I. The bias currents and transistor aspect ratios

| Table 1. The bias currents and transistor aspect ratios |             |  |  |  |  |  |  |  |

|---------------------------------------------------------|-------------|--|--|--|--|--|--|--|

| Transistor                                              | W/L (µm/µm) |  |  |  |  |  |  |  |

| Mc1, Mb1                                                | 2/0.54      |  |  |  |  |  |  |  |

| Mc2-Mc5, Mb2-Mb5, M1, M2,<br>M7, M8, MR1, MR2           | 4/0.54      |  |  |  |  |  |  |  |

| M3, M4, M9, M10                                         | 8/0.54      |  |  |  |  |  |  |  |

| M6, M12                                                 | 3.4/1       |  |  |  |  |  |  |  |

| M5, M11                                                 | 20/0.54     |  |  |  |  |  |  |  |

| Bias Current                                            | Value (nA)  |  |  |  |  |  |  |  |

| IB                                                      | 2.5         |  |  |  |  |  |  |  |

|                                                         |             |  |  |  |  |  |  |  |

Fig. 6. The open-loop voltage gain frequency response of the proposed structure

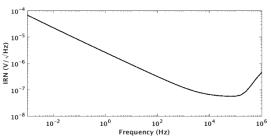

Fig. 7. The input-referred noise characteristic of proposed OTA

Fig. 8. The common-mode (a) and power supply (b) rejection characteristics of the proposed OTA

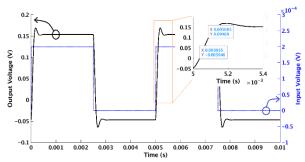

Fig. 9. The transient large-signal step response of proposed OTA in  $60\ dB$  gain configuration

The input referred noise characteristic of circuit is depicted in Fig. 7. This figure shows that the proposed structure delivers an acceptable noise performance in its

operating frequency range. The value of IRN is evaluated to be  $0.12\mu V/\sqrt{Hz}$  at frequency of 1kHz. The CMRR and PSRR performance of the proposed structure are pictured in parts (a) and (b) of Fig. 8, respectively. This figure shows that both parameters are well satisfactory. The very large value of the CMRR makes the proposed structure very suitable for circuits with biomedical applications. This mainly comes from the common-mode feedback and degeneration circuits.

The transient step-response of the proposed circuit configured in 60dB feedback gain is depicted in Fig. 9. The step size of input voltage was 0.2mV. This figure shows that the proposed structure delivers a fast rise and settling time in a stable fashion. From this figure the circuit parameters such as slew rate and settling time are extracted to be  $1.9 \text{mV}/\mu\text{s}$  and  $430\mu\text{s}$ , respectively. This relatively high value of slew rate is mainly due to the class AB operation of structure.

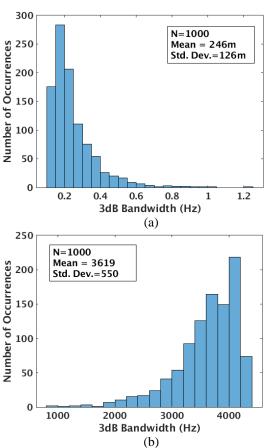

To evaluate the performance of the proposed structure against process uncertainties, the Monte Carlo simulations are conducted with 1000 runs and the results are pictured in histograms of Fig. 10 and Fig. 11. The DC voltage gain is shown in Fig. 10 (a) and the CMRR is pictured in Fig. 10 (b). The circuit simulation for open loop bandwidth is pictured in Fig. 11 (a) while the simulation for closed loop bandwidth is depicted in Fig. 11 (b). The results are very promising, showing no considerable deviation (small standard deviation,  $\sigma$ ) from the mean value,  $\mu$ .

Further investigation of circuit performance against process variations is performed by corner simulations. Therefore, the post-layout simulations are conducted in all five corners and at various operating temperatures. The simulated corners were TT, FF, SS, FS, and SF; wherein, T, F, and S stand for typical, fast and slow corners, respectively for NMOS and PMOS transistors. The results are summarized in Table II. This table includes the Monte Carlo (MC) simulation results, as well. From Table II, it can be noticed that even at the worst condition, the DC gain and CMRR parameters remain higher than 131.3dB and 135.9dB, respectively. This promises that the key parameters of the structure are well-robust against temperature and process variations. The performance parameter comparison of the proposed structure with some relevant recent works is given in Table III. From Table III, it can be noticed that the proposed OTA delivers better performance compared to most of the works in terms of some interesting merits such as DC gain, gain bandwidth, and CMRR. Therefore, the proposed OTA is best suited for low noise, low power and relatively fast applications. The following figures of merit are defined to compare the performance of the proposed structure with other work [5, 6, 24, 25].

Fig. 10. The post-layout Monte Carlo simulation results for (a) DC voltage gain, (b) CMRR

Fig. 11. The post-layout Monte Carlo simulation results for (a) Open loop bandwidth, (b) Closed loop bandwidth at 60 dB feedback gain

$$FOM_{s} = 100 \times \frac{G.BW.C_{L}}{I_{DD}} \times \frac{V_{THN} + V_{THP}}{V_{DD}}$$

(6)

$$FOM_{L} = 100 \times \frac{SR.C_{L}}{I_{DD}} \times \frac{V_{THN} + V_{THP}}{V_{DD}}$$

(7)

$$FOM_{SP} = FOM_S \times \frac{A_{v0}}{1000} \tag{8}$$

$$FOM_{LP} = FOM_L \times \frac{A_{v0}}{1000} \tag{9}$$

Comparing the performance of various works is rather hard and complex. The reason is that the circuit design procedure is a trade-off problem. Therefore, each work shows a superior performance in some parameters but fails to combat in term of other parameters. This suggests the definition and usage of some FOMs that helps to compare the overall performance of two or even more structures, appropriately. Using the presented FOMs and based on the calculated values form Table 3, the proposed

OTA outperforms the other works in three out of four defined figures of merit, including  $FOM_S$ ,  $FOM_{SP}$ ,  $FOM_{LP}$ .

Table II. The Post-layout simulation results of the OTA performance over temperature and process variations

| performance over temperature and process variations |           |       |       |           |       |       |     |  |  |  |

|-----------------------------------------------------|-----------|-------|-------|-----------|-------|-------|-----|--|--|--|

| Corner                                              | TT        | FF    | SS    | FS        | SF    | MC    |     |  |  |  |

|                                                     | @<br>27°C | @ 0°C | @     | @<br>27°C | @     | *     | σ*  |  |  |  |

|                                                     | 27°C      | @ 0°C | 85°C  | 27°C      | 27°C  | μ     |     |  |  |  |

| DC gain (dB)                                        | 141.5     | 135.8 | 134.7 | 131.3     | 134.6 | 139.2 | 3   |  |  |  |

| CMRR<br>(dB)                                        | 148.3     | 149.6 | 164.7 | 135.9     | 175.5 | 149.3 | 7.6 |  |  |  |

| PSRR+<br>(dB)                                       | 153.7     | 158.4 | 148.8 | 137.2     | 150.3 | -     | -   |  |  |  |

| PSRR-<br>(dB)                                       | 141.3     | 137   | 137.3 | 129.1     | 137.3 | -     | -   |  |  |  |

<sup>\*</sup> µ: Mean value

Table III. The summery of OTA parameters compared with some recent relevant works

| Table III. The summery of OTA parameters compared with some recent relevant works |           |       |       |       |       |       |        |       |       |       |       |       |

|-----------------------------------------------------------------------------------|-----------|-------|-------|-------|-------|-------|--------|-------|-------|-------|-------|-------|

| Parameter                                                                         | This Work | [26]  | [3]   | [5]   | [6]   | [27]  | [28]   | [29]  | [25]* | [24]* | [13]* | [30]* |

| $V_{DD}(V)$                                                                       | 0.6       | 0.5   | 0.3   | 0.4   | 0.4   | 0.5   | 0.5    | 0.6   | 0.25  | 0.3   | 0.3   | 0.9   |

| $P_{diss}(\mu W)$                                                                 | 0.15      | 0.026 | 0.051 | 2.6   | 0.3   | 28    | 0.3    | 0.4   | 0.018 | 0.017 | 0.013 | 24.3  |

| $C_{L}\left( pF\right)$                                                           | 5         | 15    | 5     | 5     | 5     | 20    | 5      | 15    | 15    | 20    | 30    | 10    |

| DC gain (dB)                                                                      | 141.5     | 67.8  | 60    | 72.6  | 81.37 | 65    | 60     | 82    | 60    | 65.8  | 64.7  | 65    |

| Open loop<br>BW (Hz)                                                              | 1.83      | 1.33  | 70    | 76.6  | 23.9  | 309   | 27     | 1.5   | 1.88  | 1.4   | 1.68  | 562   |

| PM (°)                                                                            | 60**      | 68.9  | 53    | 56    | 59.2  | 50    | 69     | 60    | 52.5  | 61    | 52    | 60    |

| SR<br>(mV/µs)                                                                     | 1.9       | 0.84  | 25    | 212   | 125   | 230   | -      | 12    | 0.77  | 7.1   | 1.9   | 250   |

| IRN                                                                               |           |       |       |       |       |       | 2000   |       |       |       |       |       |

| $(nV/\sqrt{Hz})$                                                                  | 121.8     | 560   | 2820  | 173   | 213   | 432   | @      | 160   | #3300 | _     | _     | 65    |

| at 1kHz                                                                           |           |       |       |       |       |       | 0.1kHz |       |       |       |       |       |

| CMRR<br>(dB)                                                                      | 148.3     | -     | 126   | 110.7 | 126   | 86    | 53.15  | 130   | -     | 72    | 110   | 45    |

| PSRR (dB)                                                                         | 153.7     | -     | 91    | 103   | 79.1  | 76    | -      | -     | -     | 62    | 56    | 55    |

| 1% Ts (μs)                                                                        | 430       | 635   | 49.4  | 6.4   | 11    | -     | -      | -     | -     | 104   | 446   | 1.8   |

| Area (mm <sup>2</sup> )                                                           | 0.006     | -     | 0.003 | 0.013 | 0.005 | 0.052 | -      | -     | 0.083 | 0.008 | 0.008 | 0.014 |

| $FOM_S$ $(V^{-1})$                                                                | 72666     | 188   | 411   | 63    | 467   | 39.3  | 45     | 60    | 67.4  | 349   | 669   | 561   |

| $FOM_L$ $(V^{-1})$                                                                | 6.3       | 48.4  | 245   | 41    | 208   | 16.4  | -      | 45    | 36.8  | 856   | 438   | 140   |

| $FOM_{SP}$ $(V^{-1})$                                                             | >863*10^6 | 451   | 411   | 271   | 5468  | 66.8  | 45     | 750   | 67.4  | 680   | 1149  | 997   |

| $FOM_{LP}$ $(V^{-1})$                                                             | >73000    | 116.1 | 411   | 168.6 | 2435  | 113.6 | -      | 562.5 | 36.8  | 1669  | 752   | 249   |

| Technology (nm)                                                                   | 180       | 180   | 65    | 180   | 180   | 180   | 180    | 180   | 130   | 180   | 180   | 350   |

<sup>\*</sup> Measurement results

<sup>\*</sup> σ: Standard deviation

<sup>#</sup> Thermal Noise

<sup>\*\*</sup> for 60dB voltage gain

# 4. Conclusion

A High-gain, fully-balanced preamplifier was presented in this paper. The proposed structure advantages flipped voltage follower scheme to achieve a compact current conveyor with very low input impedance. The presented current conveyor was used as a core element to realize a high-gain, gm-enhanced trans-conductance amplifier. The Spectre Post-layout simulations with TSMC 180nm CMOS technology file have been performed to validate the performance of the proposed amplifier. The proposed amplifier exhibits an open loop DC gain of 141.5dB and 3-dB frequency bandwidth of 2.4kHz at 60dB closed-loop configuration. The load capacitance is set to be 5pF. The proposed structure also delivers high CMRR and PSRR values of 148.3dB and 153.7dB, respectively. To investigate the performance of the design over process and temperature variations, the Monte Carlo and corner simulations are performed.

#### References

- [1] A. Fahim, "Challenges in low-power analog circuit design for sub-28nm CMOS technologies," in 2014 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), 11-13 Aug. 2014 2014, pp. 123-126, doi: 10.1145/2627369.2631639.

- [2] W. Sansen, "Analog design challenges in nanometer CMOS technologies," in 2007 IEEE Asian Solid-State Circuits Conference, 12-14 Nov. 2007 2007, pp. 5-9, doi: 10.1109/ASSCC.2007.4425792.

- [3] H. Veldandi and R. A. Shaik, "A 0.3-V Pseudo-Differential Bulk-Input OTA for Low-Frequency Applications," *Circuits, Systems, Signal Processing*, vol. 37, no. 12, pp. 5199-5221, 2018.

- [4] S. Sadeghi, M. Nayeri, M. Dolatshahi, and A. Moftakharzadeh, "Novel Ultra-Low-Power Mirrored Folded-Cascode Transimpedance Amplifier," *Journal of Electrical and Computer Engineering Innovations (JECEI)*, vol. 11, no. 1, pp. 217-228, 2023, doi: 10.22061/jecei.2022.9015.568.

- [5] H. Faraji Baghtash, "A 0.4 V, tail-less, fully differential trans-conductance amplifier: an all inverter-based structure," *Analog Integrated Circuits and Signal Processing*, vol. 104, no. 1, pp. 1-15, 2020/07/01 2020, doi: 10.1007/s10470-020-01662-5.

- [6] H. Faraji Baghtash, "A 0.4 V, body-driven, fully differential, tail-less OTA based on current push-pull," *Microelectronics Journal*, vol. 99, p. 104768, 2020/05/01/ 2020, doi: <a href="https://doi.org/10.1016/j.mejo.2020.104768">https://doi.org/10.1016/j.mejo.2020.104768</a>.

- [7] K. Monfaredi and H. Faraji Baghtash, "An Extremely Low-Voltage and High-Compliance Current Mirror," *Circuits, Systems, and Signal Processing*, 2019/06/20 2019, doi: 10.1007/s00034-019-01175-1.

- [8] R. Sanati, F. Khatib, M. Javadian Sarraf, and R. Kardehi Moghaddam, "Low Power Bulk-Driven Time-Domain Comparator with High Voltage-to-Time Gain," *Tabriz Journal of Electrical Engineering*, vol. 51, no. 4, pp. 393-401, 2022. [Online]. Available: <a href="https://tjee.tabrizu.ac.ir/article-14817-9188a938a1095e0ea-051ccb71876ce5d.pdf">https://tjee.tabrizu.ac.ir/article-14817-9188a938a1095e0ea-051ccb71876ce5d.pdf</a>.

- [9] H. Faraji Baghtash, "Mismatch Tolerant, Wide Bandwidth Current Mirror," *Tabriz Journal of Electrical Engineering*, vol. 48, no. 1, pp. 231-236, 2018. [Online]. Available: <a href="https://tjee.tabrizu.ac.ir/article-7461-4aef6a02790b1cf9d2e">https://tjee.tabrizu.ac.ir/article-7461-4aef6a02790b1cf9d2e</a> <a href="bbe882a41ce5a.pdf">bbe882a41ce5a.pdf</a>.

- [10] F. Khateb, T. Kulej, H. Veldandi, and W. Jaikla, "Multiple-input bulk-driven quasi-floating-gate MOS transistor for low-voltage low-power integrated circuits,"

- AEU-International Journal of Electronics Communications, vol. 100, pp. 32-38, 2019.

- [11] T. Dubey and V. Bhadauria, "A low-voltage highly linear OTA using bulk-driven floating gate MOSFETs," *AEU International Journal of Electronics and Communications*, vol. 98, pp. 29-37, 2019/01/01/2019, doi: https://doi.org/10.1016/j.aeue.2018.10.034.

- [12] D. N. Jagadish and M. S. Bhat, "A Low Voltage Inverter Based Differential Amplifier for Low Power Switched Capacitor Applications," in 2014 Fifth International Symposium on Electronic System Design, 15-17 Dec. 2014 2014, pp. 58-62, doi: 10.1109/ISED.2014.20.

- [13] T. Kulej and F. Khateb, "A Compact 0.3-V Class AB Bulk-Driven OTA," *IEEE Transactions on Very Large Scale Integration Systems*, 2019.

- [14] R. Nagulapalli, K. Hayatleh, and S. Barker, "A Positive Feedback-Based Op-Amp Gain Enhancement Technique for High-Precision Applications," *Journal of Circuits, Systems and Computers*, vol. 29, no. 14, p. 2050220, 2020, doi: 10.1142/s0218126620502205.

- [15] M. Parvizi, K. Allidina, and M. N. El-Gamal, "Short Channel Output Conductance Enhancement Through Forward Body Biasing to Realize a 0.5 V 250 uW 0.6–4.2 GHz Current-Reuse CMOS LNA," *IEEE Journal of Solid-State Circuits*, vol. 51, no. 3, pp. 574-586, 2016, doi: 10.1109/JSSC.2015.2504413.

- [16] Y. Li, K. Han, X. Tan, N. Yan, and H. J. E. l. Min, "Transconductance enhancement method for operational transconductance amplifiers," *Electronics Letters*, vol. 46, no. 19, pp. 1321-1323, 2010.

- [17] X. Zhao, Q. Zhang, Y. Wang, M. J. A.-I. J. o. E. Deng, and Communications, "Transconductance and slew rate improvement technique for current recycling folded cascode amplifier," AEU International Journal of Electronics and Communications, vol. 70, no. 3, pp. 326-330, 2016.

- [18] J. M. Carrillo, G. Torelli, J. J. A. I. C. Duque-Carrillo, and S. Processing, "Transconductance enhancement in bulkdriven input stages and its applications," *Analog Integrated Circuits and Signal Processing*, vol. 68, no. 2, pp. 207-217, 2011

- [19] Q. Zhang, X. Zhao, X. Zhang, Q. J. A.-I. J. o. E. Zhang, and Communications, "Multipath recycling method for transconductance enhancement of folded cascade amplifier," AEU International Journal of Electronics and Communications, vol. 72, pp. 1-7, 2017.

- [20] M. Akbari, S. Biabanifard, S. Asadi, M. C. J. A.-I. J. o. E. Yagoub, and Communications, "Design and analysis of DC gain and transconductance boosted recycling folded cascode OTA," AEU International Journal of Electronics and Communications, vol. 68, no. 11, pp. 1047-1052, 2014.

- [21] M. Menon, K. Dhall, A. Gupta, and N. Chaturvedi, "Low power cascaded three stage amplifier with multipath nested miller compensation," in 2010 International Conference on Recent Trends in Information, Telecommunication and Computing, 2010: IEEE, pp. 9-12.

- [22] S. Biabanifard, S. M. Largani, A. Biamanifard, M. Biabanifard, M. Hemmati, and Z. Khanmohammadi, "Three stages CMOS operational amplifier frequency compensation using single Miller capacitor and differential feedback path," *Analog Integrated Circuits and Signal Processing*, vol. 97, no. 2, pp. 195-205, 2018/11/01 2018, doi: 10.1007/s10470-018-1117-5.

- [23] W.-S. Tam and C.-W. Kok, "Design methodology of double nulling resistors nested-Miller compensation of multistage amplifier," *Solid State Electronics Letters*, vol. 1, no. 1, pp. 15-24, 2019/01/01/ 2019, doi: <a href="https://doi.org/10.1016/j.ssel.2018.06.001">https://doi.org/10.1016/j.ssel.2018.06.001</a>.

- [24] T. Kulej and F. Khateb, "Design and implementation of sub 0.5-V OTAs in 0.18-µm CMOS," *international*

- *Journal of Circuit Theory and Applications*, vol. 46, no. 6, pp. 1129-1143, 2018, doi: 10.1002/cta.2465.

- [25] L. H. C. Ferreira and S. R. Sonkusale, "A 60-dB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 6, pp. 1609-1617, 2014, doi: 10.1109/TCSI.2013.2289413.

- [26] X. Zhao, H. Fang, T. Ling, and J. J. I. Xu, "Transconductance improvement method for low-voltage bulk-driven input stage," *Integration The VLSI Journal*, vol. 49, pp. 98-103, 2015.

- [27] M. Trakimas and S. Sonkusale, "A 0.5 V bulk-input OTA with improved common-mode feedback for low-frequency filtering applications," *Analog Integrated Circuits and Signal Processing*, journal article vol. 59, no. 1, pp. 83-89, April 01 2009, doi: 10.1007/s10470-008-9236-z.

- [28] N. Suda, P. V. Nishanth, D. Basak, D. Sharma, and R. P. Paily, "A 0.5-V low power analog front-end for heart-rate detector," *Analog Integrated Circuits and Signal Processing*, journal article vol. 81, no. 2, pp. 417-430, November 01 2014, doi: 10.1007/s10470-014-0402-1.

- [29] M. Akbari and O. Hashemipour, "A 0.6-V, 0.4-μW bulk-driven operational amplifier with rail-to-rail input/output swing," *Analog Integrated Circuits Signal Processing*, vol. 86, no. 2, pp. 341-351, 2016.

- [30] A. D. Grasso, S. Pennisi, G. Scotti, and A. Trifiletti, "0.9-V Class-AB Miller OTA in 0.35-μm CMOS With Threshold-Lowered Non-Tailed Differential Pair," *IEEE Transactions on Circuits Systems I: Regular Papers*, vol. 64, no. 7, pp. 1740-1747, 2017.